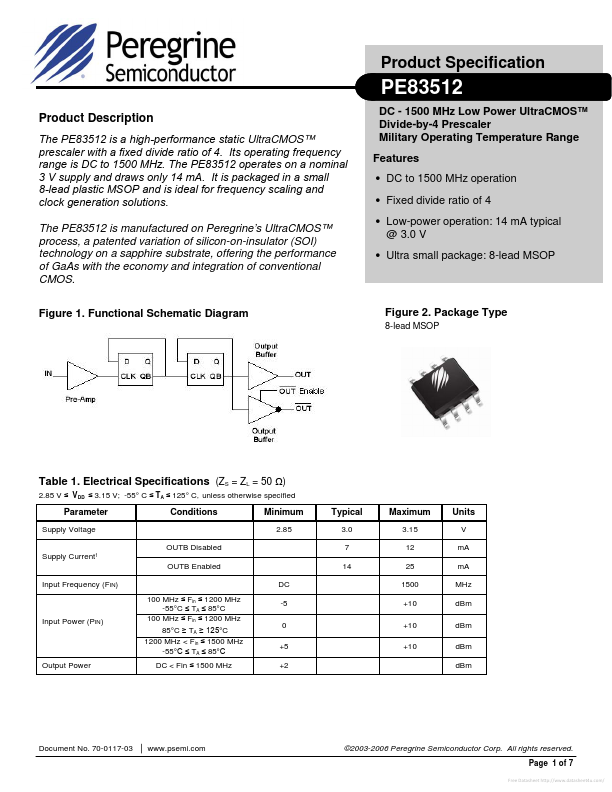

| Part | PE83512 |

|---|---|

| Description | DC - 1500 MHz Low Power UltraCMOS |

| Manufacturer | pSemi |

| Size | 288.43 KB |

Similar Parts

| Part Number | Manufacturer | Description |

|---|---|---|

| PE4257 | pSemi | SPDT Absorptive UltraCMOS DC 3.0GHz RF Switch |

| PE42445 | pSemi | High Isolation UltraCMOS SP4T RF Switch |

| PE42420 | pSemi | UltraCMOS SPDT RF Switch |